How to invert a signal quartus – Kicking off with how to invert a signal in Quartus, this opening paragraph is designed to captivate and engage the readers, setting the tone that unfolds with each word. Inverting a signal in Quartus is a crucial step in digital circuit design, and mastering this technique can greatly benefit designers looking to optimize their circuit’s performance.

The provided Artikel walks through the entire process, starting from defining the requirements for signal inversion in Quartus to optimizing inverter performance in Quartus HDL. Designers will learn about the different methods of signal inversion available in Quartus, including using the Altera IP library or generating a custom IP block. They will also discover the techniques for optimizing inverter performance, such as using pipelining, retiming, and optimizing clock domains.

Defining the Requirements for Signal Inversion in Quartus

When working with digital circuits in Quartus, it’s essential to understand signal inversion concepts. Inversion involves changing the logic state of a signal to ensure proper circuit operation and prevent issues like glitches or incorrect outputs.

Signal inversion may be necessary when you need to change the logic state of a signal, such as when the desired output is the inverse of the input. For instance, you might need to invert a signal when you’re trying to implement an XOR gate, which produces an output that is the inverse of the sum of the inputs.

Determining the Correct Inversion Method

In Quartus, you can use various methods to invert signals, depending on the specific requirements of your project and the characteristics of the signals involved. Here are a few common inversion methods and their applications:

To determine the correct inversion method, you’ll need to consider the type of signal you’re working with. For example:

-

You can use a simple inverter gate when working with digital signals that need to be inverted. A simple inverter is an example of an elementary logic gate, typically represented by a single NOT gate. For instance, a single NOT gate might look like this:

NOT A

- When dealing with complex digital signals, you might need to use more advanced inversion methods. In these cases, you can use combination logic, which involves combining multiple logic gates to achieve the desired output. This approach allows for more flexibility and can be useful when working with signals that have multiple inputs or complex logic operations.

In general, you should use the inversion method that best suits the characteristics of your signals and the requirements of your project.

Importance of Signal Inversion

Signal inversion is crucial in digital circuit design, as it plays a key role in ensuring proper circuit operation and preventing issues like glitches or incorrect outputs. Here are some reasons why signal inversion is important:

- Signal inversion helps to prevent issues like glitches or incorrect outputs by changing the logic state of the signal to match the desired output.

- Signal inversion is necessary when implementing logic gates that produce an inverse output, such as XOR or XNOR gates.

Incorrect inversion can lead to issues like:

- Glitches or incorrect outputs due to mismatched logic states.

- Inaccurate circuit operation due to incorrect signal inversion.

In summary, signal inversion is a critical aspect of digital circuit design, and understanding the various inversion methods and their applications is essential for ensuring accurate and reliable circuit operation.

Inverting Signals in Quartus using Altera IP

Inverting signals in Quartus is a crucial step in many digital design projects, especially when working with Altera IPs. This method allows you to easily invert signals using the Altera IP library, which can save you a significant amount of time and effort.

Inverter is an Altera IP that simply flips the bits of its input. This is useful when the truth table of a design contains an inverter. Inverter accepts a single input and produces a single output signal that is inverted. This is equivalent to a NOT gate in digital logic.

There are two main methods to invert signals in Quartus using Altera IP: using the Altera IP library or generating a custom IP block. Here’s a comparison of the two methods:

Using the Altera IP Library

This method involves using the Altera IP library, which provides a variety of pre-designed blocks that can be instantiated in your design. The inverter is one of these blocks, and it can be used to invert a signal in a single step.

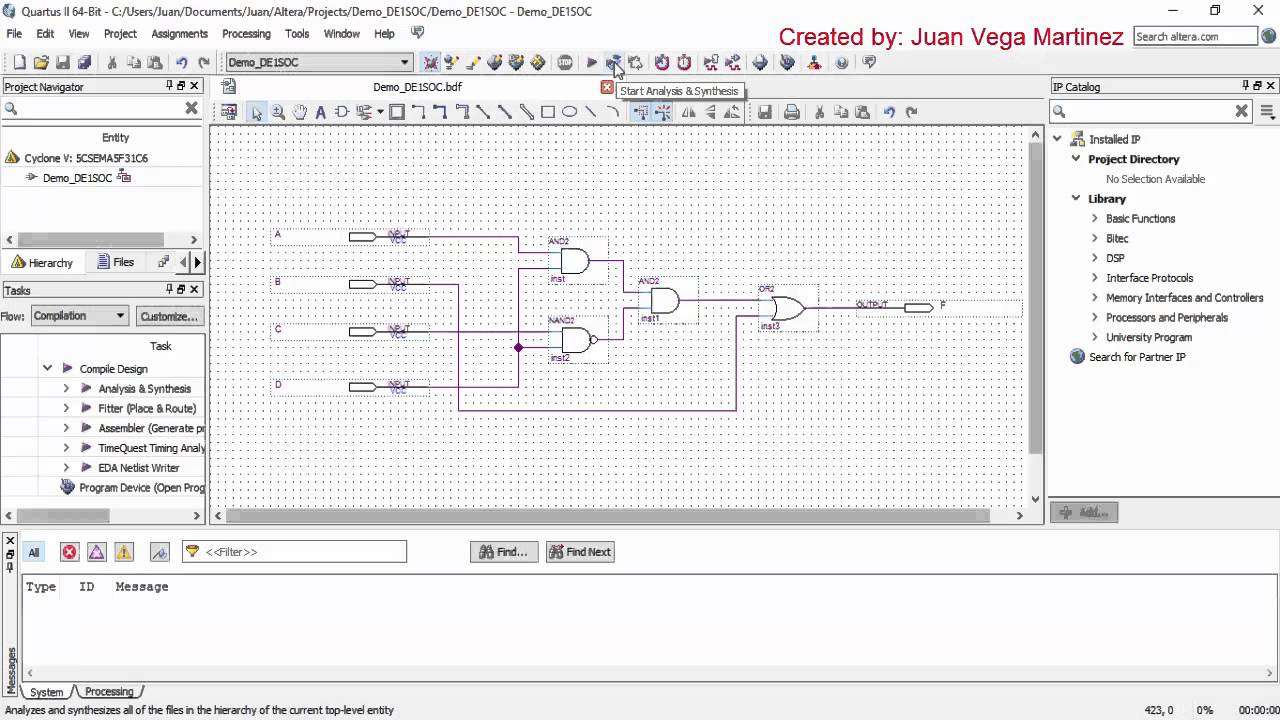

To use the Altera IP library, follow these steps:

- Open your Quartus project and go to the “IP Wizard” menu.

- Select “Altera IP” from the list of available IP cores.

- Navigate to the “Logic Elements” category and select the “Inverter” block.

- Drag and drop the inverter block into your design.

- Connect the input signal to the inverter block and the output signal to the rest of your design.

This method is simple and easy to use, and it’s a good option when you need to invert a signal in a hurry.

The Altera IP library has an advantage over other methods in terms of speed and convenience. The library contains a wide range of pre-designed blocks, including the inverter, which can save you a significant amount of time and effort.

However, this method has some limitations:

- You need to have a Quartus project set up and running.

- You need to have the Altera IP library installed and configured.

- You need to have a good understanding of the Altera IP library and how to use it.

In summary, using the Altera IP library is a simple and straightforward way to invert signals in Quartus, but it requires some setup and configuration beforehand.

Generating a Custom IP Block

This method involves creating a custom IP block to invert a signal. This can be a more complex process, but it gives you more control over the design and allows you to customize the inverter to meet your specific needs.

To generate a custom IP block, follow these steps:

- Open your Quartus project and go to the “IP Wizard” menu.

- Select “Custom IP” from the list of available IP cores.

- Navigate to the “Logic Elements” category and select the “Inverter” block.

- Create a new IP block by dragging and dropping the inverter block into your design.

- Configure the IP block to meet your specific needs.

This method requires more expertise and effort, but it gives you more control over the design and allows you to customize the inverter to meet your specific needs.

This method has the advantage of giving you more control over the design, but it requires more expertise and effort to set up and configure.

In summary, generating a custom IP block is a more complex process that requires more expertise and effort, but it gives you more control over the design and allows you to customize the inverter to meet your specific needs.

Advantages and Limitations of Each Method

Using the Altera IP library has the advantages of speed and convenience, but it requires some setup and configuration beforehand. Generating a custom IP block has the advantage of giving you more control over the design, but it requires more expertise and effort to set up and configure.

Designing a Custom Inverter in Quartus

Designing a custom inverter in Quartus requires careful consideration of several factors, including component selection, inverter performance optimization, and integration with the overall circuit design. Creating a custom inverter can be beneficial for specific applications where standard inverter components are not sufficient or suitable.

Design Considerations

When designing a custom inverter in Quartus, some key considerations include:

- Choosing the right logic element: Quartus provides various logic elements, such as lookup tables (LUTs) and programmable logic arrays (PLAs), which can be used to implement custom inverters.

- Optimizing inverter performance: The inverter’s performance can be optimized by adjusting the timing and resources of the circuit, which may involve trade-offs between speed and area.

- Ensuring noise immunity: The inverter should be designed to be robust against noise and other forms of signal degradation to ensure reliable operation.

Example Design for Simple Inverter

A simple inverter can be designed using a single LUT. Here’s an example design:

| Component | Description |

|---|---|

| LUT | A 2-input LUT can be used to implement a simple inverter by setting the output to the complement of the input. |

| CLOCK | A clock signal can be used to synchronize the inverter’s operation. |

Example code for the simple inverter in Quartus:

module inverter(clk, in, out); input clk, in; output out; assign out = ~in; endmodule

This design uses a single LUT to implement the inverter, and the clock signal is used to synchronize the operation. The inverter’s output is simply the complement of the input.

Understanding the Interaction of Inverters and Clock Signals in Quartus

When working with digital circuits, understanding how inverters interact with clock signals is crucial, especially in Quartus where signal inversion can significantly impact design complexity and timing.

“Clock domain crossings” refers to situations where signals from different clock domains must be transferred to a different clock domain.

Clock domain crossings can occur when signals from one clock domain are being processed in a different clock domain. Inverters can play a significant role in managing these crossings by either synchronizing or desynchronizing the signals.

Clock Synchronization with Inverters

To synchronize signals across different clock domains, inverters can be used to create a common clock domain. This is achieved by synchronizing the signals using a clock signal that is common to all clock domains.

- When using inverters for clock synchronization, it is essential to ensure that the inverter is properly connected to the clock signal. The inverter should be connected to the clock signal as close to the source as possible.

- The inverter should also be synchronized with the clock signal, ensuring that it is triggered at the same time as the clock signal.

- The signal being inverted should also be properly synchronized with the clock signal, ensuring that it is triggered at the same time as the clock signal.

Managing Clock Domain Crossings

In addition to clock synchronization, inverters can also be used to manage clock domain crossings by desynchronizing signals. This is achieved by using a clock signal from one clock domain to invert the signal from another clock domain.

A common approach to managing clock domain crossings is to use a “clock domain crossing” (CDC) component.

CDC components can be used to synchronize and desynchronize signals, making them an essential tool in managing clock domain crossings.

Design Considerations

When managing clock domain crossings using inverters, several design considerations must be taken into account.

- Ensure that the inverter is properly connected to the clock signal and that it is synchronized with the clock signal.

- Ensure that the signal being inverted is properly synchronized with the clock signal.

- Use CDC components to manage clock domain crossings and ensure that signals are properly synchronized.

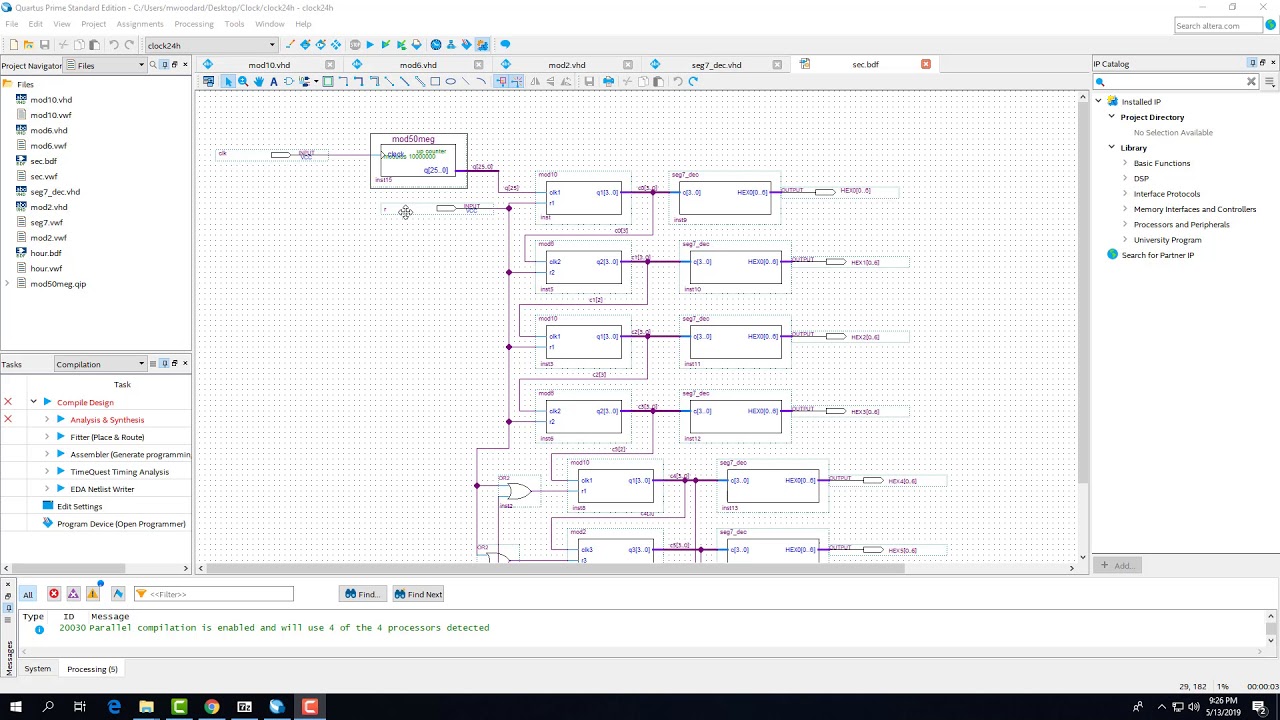

Using Logic Hierarchy to Simplify Signal Inversion in Quartus

In Quartus, signal inversion can be a complex task, especially when dealing with multiple signals and their interactions. However, the logic hierarchy feature can simplify this process by abstracting away low-level details and providing a more structured approach to signal manipulation.

The logic hierarchy in Quartus allows users to create a hierarchical representation of their design, breaking it down into smaller blocks or modules. This abstraction can greatly simplify signal inversion by making it easier to target specific signals and their interactions without getting bogged down in the intricacies of individual logic gates.

Example of Using Logic Hierarchy for Signal Inversion

To illustrate this point, let’s consider an example where we have a complex digital circuit consisting of multiple logic gates and signals. We need to invert a specific signal, say “A”, while minimizing the impact on other signals in the circuit.

- First, create a new hierarchy level in Quartus to represent the block of logic related to signal “A”.

- Within this block, create a new module that specifically deals with signal inversion.

- Use the logic hierarchy to connect the module to the relevant input and output signals, allowing you to target signal “A” directly.

- Apply the signal inversion logic within the module, using standard logic gates and operations.

- Finally, use the Quartus simulation tools to verify that the inverted signal “A” behaves as expected within the larger circuit.

Using the logic hierarchy in this way allows us to isolate the signal inversion logic from the rest of the circuit, making it easier to modify and test. By abstracting away low-level details, we can focus on the high-level design and optimization of our digital circuit.

“The logic hierarchy feature in Quartus provides a powerful tool for simplifying signal inversion and other complex digital signal manipulation tasks.”

Best Practices for Implementing Inverters in Quartus Designs

As we’ve discussed the different methods for inverting signals in Quartus, it’s essential to remember some best practices that will help you to design and implement inverters efficiently. By following these guidelines, you’ll be able to ensure that your inverter performance meets specific requirements and minimizes potential errors.

Optimize Your Inverter Design

When designing an inverter, it’s crucial to optimize your circuit for performance and area efficiency. One way to do this is by utilizing Quartus’s built-in optimization tools, which can help reduce the area required by your inverter and improve its overall performance. Additionally, when designing your inverter, consider using a hierarchical design approach, where you break down your circuit into smaller, more manageable blocks. This will make it easier to optimize each block independently and ensure that your overall design is optimized.

Use Quartus’s Built-in Resources

Quartus provides a wide range of built-in resources that can be used to implement inverters efficiently. For example, the Altera IP catalog includes a variety of pre-designed inverters that can be used in your design. Additionally, Quartus’s built-in logic synthesis tools can help optimize your inverter design and minimize area.

Minimize Fanout and Signal Switching

Fanout and signal switching can significantly impact the performance of your inverter design. To minimize these effects, make sure to keep your design as simple as possible and avoid unnecessary signal switching. One way to do this is by using Quartus’s built-in optimization tools, which can help reduce fanout and signal switching in your design.

Use a Consistent Design Style

Consistency is key when it comes to designing and implementing inverters in Quartus. To ensure that your design is consistent and easy to manage, establish a clear design style that includes naming conventions, coding standards, and other best practices. This will help make your design more maintainable and ensure that your inverters are implemented correctly.

Test and Verify Your Design, How to invert a signal quartus

Finally, it’s essential to test and verify your inverter design before releasing it into production. Use Quartus’s built-in simulation tools to test your design and ensure that it meets your performance requirements. Additionally, consider using formal verification tools to formally prove the correctness of your design.

| Design Consideration | Best Practice |

|---|---|

| Optimize Your Inverter Design | Use Quartus’s built-in optimization tools and hierarchical design approach |

| Minimize Fanout and Signal Switching | Avoid unnecessary signal switching and use Quartus’s built-in optimization tools |

| Use a Consistent Design Style | Establish clear design style that includes naming conventions, coding standards, and other best practices |

| Test and Verify Your Design | Use Quartus’s built-in simulation tools and formal verification tools |

Conclusion: How To Invert A Signal Quartus

In conclusion, inverting a signal in Quartus is a fundamental aspect of digital circuit design that requires a clear understanding of the various methods and techniques available. By mastering signal inversion in Quartus, designers can create more efficient and reliable circuits that meet specific requirements. Remember to follow the best practices for implementing inverters in Quartus designs and verify signal inversion using formal or informal verification methods.

FAQ Overview

What is the most efficient method for inverting a signal in Quartus?

The most efficient method for inverting a signal in Quartus depends on the specific design requirements and signal characteristics. However, using the Altera IP library is often a great starting point, as it provides a pre-verified and optimized solution.

How do I optimize inverter performance in Quartus HDL?

To optimize inverter performance in Quartus HDL, designers can use techniques such as pipelining, retiming, and optimizing clock domains. Additionally, they can use the Quartus synthesis tool to further optimize inverter performance.

What is the importance of verifying signal inversion in Quartus?

Verifying signal inversion in Quartus is crucial to ensure that the inverter is operating correctly and meeting specific requirements. Incorrect inverter operation can lead to system failures and compromised performance.